Reducing signal degradation requires dielectrics with lower Dk and LT, more metal and conductors without rough surfaces.

At a trade show a few years ago, our Simberian booth was next to a booth with a very loud demonstration transferring 112Gbps over a distance of about one meter through cables. I don’t know how many terabytes of data they transferred during the show, but the demonstration equipment was noisy because of the industrial cooling equipment. I could feel the heat coming out of it. The devices were transferring data and not much else. How much energy is required to transmit data, and why is so much power dissipated into heat, I wondered.

PCB interconnects degrade digital signals. Signals may be reflected, coupled to other interconnects, or to power distribution structures or free space, but most important, conductors and dielectrics always absorb the signal energy and dissipate or turn it into heat. This article is about signal degradation due to the inevitable absorption and dispersion caused by dielectrics and conductors. How much energy does it take to transmit one bit of information, and where does this energy eventually go?

Energy Per Bit

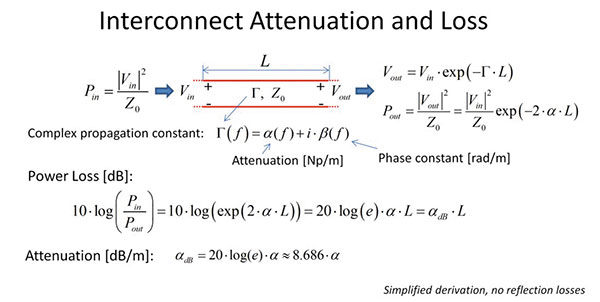

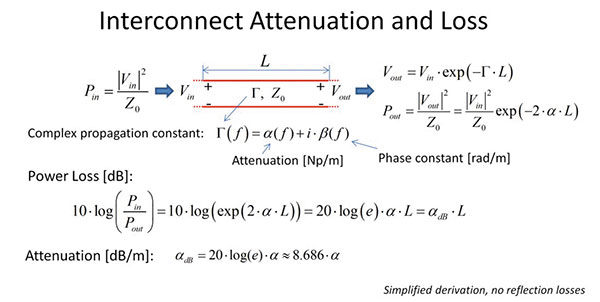

Let’s begin with the evaluation of energy absorbed (or dissipated) by copper interconnects. The power delivered to a 100Ω differential transmission line with 1V signal amplitude is 10mW. It doubles to 20mW if the transmitter source termination resistor is considered. Let’s assume the link is ideally designed, as in FIGURE 1, with no reflections and coupling. (Such links can indeed be designed.) The remaining signal degradation factor is the absorption or dissipation, losses in conductors and dielectrics, and dispersion related to it.

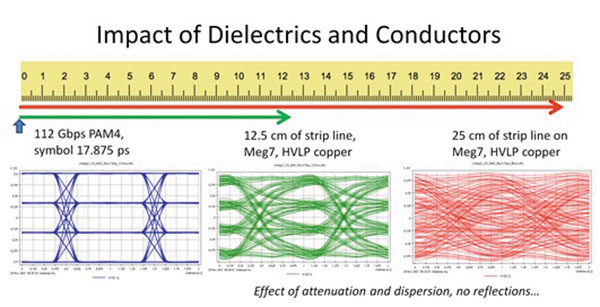

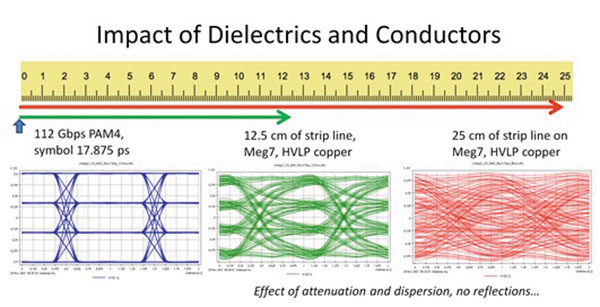

Figure 1. 112Gbps PAM4 signal degradation in a typical PCB interconnect due to absorption in dielectrics and conductors.

So, if the link insertion loss due to absorption at the Nyquist frequency (half the bit rate for the NRZ signal) is -20dB, then we have 0.1mW at the receiver end (0.1V, 100Ω). Note receivers on some expensive components allow -30dB (0.032V, 10uW) and -40dB (0.01V, 1uW) loss at the Nyquist frequency. For our evaluation, however, it doesn’t matter because the signal at the receiver end is also converted into heat at the termination resistor. All signal energy is converted into heat.

For a 50Gbps NRZ signal with 20ps unit interval, the energy converted into heat in a differential link with termination resistors is about 0.4pJ/bit (20mW x 20psec – product of power and bit time). This is practically an immutable bottom level. We cannot reduce the energy per bit in the copper interconnects under the assumptions provided above (1V, 100Ω). 20mW of power or 0.4pJ/bit for 50Gbps NRZ signal – is it small or not? It would take almost 929 hours to boil one cup of water. (Heat 200g of water from 20 to 100°C.) Admittedly, it does not look like much heat. However, this is just one link, and internet routers or switches may have more than 1,000 such links. That is enough to have a cup of tea in about an hour. This is still not impressive.

But this is not the end of the story. When equalization is included, the actual cost of a bit transfer on a PCB for 50Gbps is at least an order of magnitude larger. It is about 5pJ/bit (or 250mW) for 50Gbps NRZ.1 With a thousand links, this is enough to prepare a cup of tea in five minutes, and the IOs on chip dissipate about 90% of this energy.

Does this explain the industrial cooling equipment for 112Gbps links? I haven’t seen the power consumption data for 112Gbps or the upcoming 224Gbps links. (Email me if you have it.) But, following the recent trends (doubling data rate increases required power by 30%), it should be about 6.5pJ/bit (325mW) for 112Gbps and 8.45pJ/bit (422mW) for 224Gbps.

The number of IOs does not increase at the same time. That may be the clue. Also, the prototype equipment may be much less efficient. On the bright side, some recent developments in this area promise to reduce the numbers to about 2pJ/bit or 100mW2.

Why do we need so much power? To mitigate the signal degradation in interconnects between the driver and receiver. Transmitters and receivers are not two transistor devices in serial interconnects; they contain hundreds (maybe thousands) of transistors, and most of the energy is spent generating and restoring the signal. Can we reduce the power by design of interconnects? The answer is absolutely yes – by reducing the signal degradation in interconnects!

Energy Loss in Dielectrics

In general, more power and more expensive components are required for interconnects with larger losses or overall signal distortion, and lower power is needed for interconnects with smaller losses and distortions.

At DesignCon 20203, we discussed the major signal degradation factors and how to reduce them or design “transparent” or “clean” interconnects. The degradation factors can be broken into three categories: 1) absorption or dissipation by conductors and dielectrics and dispersion related to that; 2) reflections; and 3) coupling.

We called the first category “thermal losses” because the signal energy is literally heating the interconnect materials. Though, maybe “absorption” or “dissipation losses” are better terms.

When performing interconnect modeling, the following questions should be answered: What effects are important at a particular data rate? Does signal integrity software account for them? If all effects are included, will the model correlate with measurements?

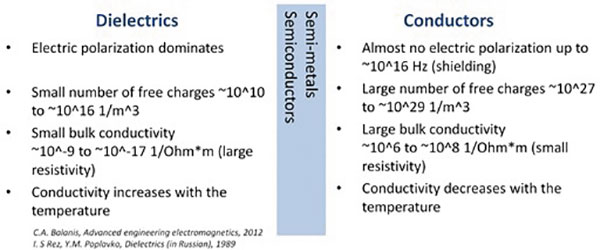

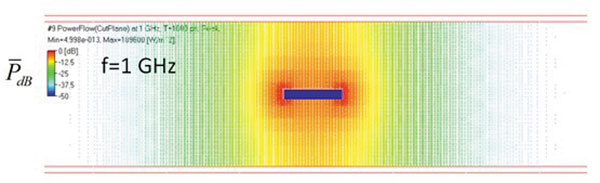

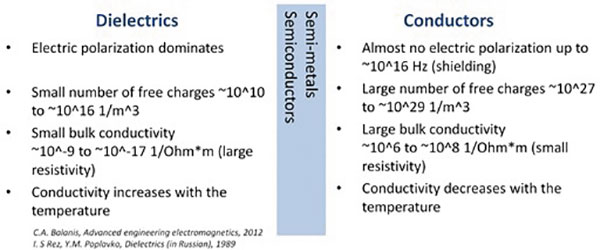

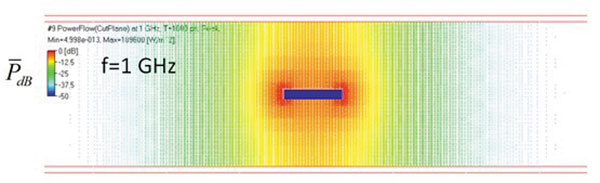

Electrical properties of dielectric and conductive materials are outlined in FIGURE 2. Let’s start with the energy absorbed (or dissipated) by dielectrics and the dispersion related to it. Why does the dielectric matter? Because the signal energy propagates along the PCB and packaging interconnects mostly in the dielectrics around the signal conductors. As Ralph Morrison points out, “Energy travels in the spaces, not in the traces.”4 The signal energy location can be illustrated with the peak power density flow (PDF), a vector product of electric and magnetic fields. For a typical PCB stripline interconnect (FIGURE 3), the color scale is used to plot peak power flow density (PFD) in W/m^2 (shown in dB), computed with Simbeor THz.

Figure 2. Properties of dielectrics and conductors.

Figure 3. Power flow density in a typical PCB stripline interconnect (strip 1.2-mil thick, 7-mil wide, DK = 3.76, LT = 0.006 @ 1GHz, planes 0.77-mil thick, 17.2-mil apart).

The signal energy concentrates near the strip edges and between the strip and planes in the dielectric. The PDF is directed along the conductors into the picture. No power is actually moving in the direction of the signal within the conductors. All dielectrics absorb or dissipate the energy.2 It is important to understand this.

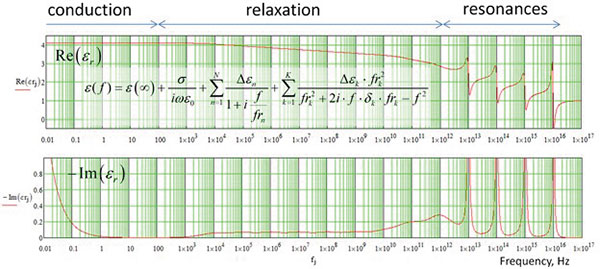

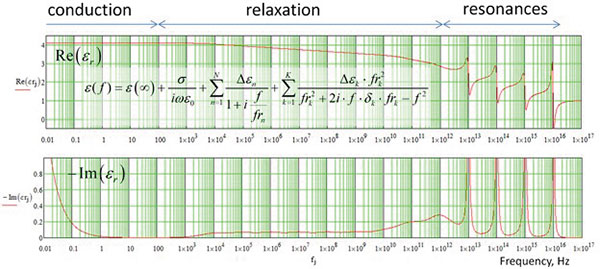

In general, dielectric properties can be described with the permittivity that is a complex function of frequency – always for real materials! We call the real part of the permittivity the dielectric constant (Dk). The ratio of the negative imaginary part of permittivity to the real part is called loss tangent (LT) or dissipation factor (DF). It describes the power loss to heat and dispersion. A universal dielectric model may look like the one in FIGURE 4.

Figure 4. A universal dielectric model: the real part (top graph) and the negative imaginary part (bottom graph).

The model in Figure 4 is of a real material constructed from fitting measured data up to 50GHz and guessed above it. This shows the different mechanisms contributing to the losses in dielectrics (imaginary part of permittivity) and dispersion.

The conduction losses for the dielectric materials in the PCB and packaging dielectrics are negligibly small. They are responsible for the increase of the imaginary part below 100Hz. (This is not a typo.) There are very few free charges in the dielectrics, such as ionic carriers.

At frequencies up to 1THz, we are dealing with the relaxation of losses related to electronic polarization of atoms (RC circuit type – no oscillations). That is modeled as either multipole Debye or wideband Debye models4. That also means the Dk can only decrease with the frequency at these frequencies. We are dealing with composite solids here, mostly polymers. Lorentzian terms (oscillating RLC circuit type) are added for illustrative purposes to show the resonant properties of the solid PCB materials are important over 1THz, where Dk may go down because of the resonances.

A Causal Material Model

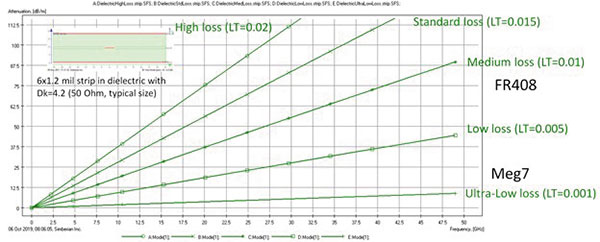

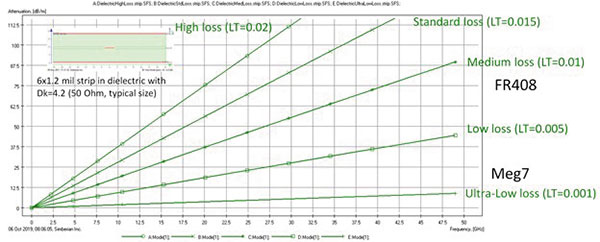

At “normal” frequencies up to 100GHz, dielectric polarization losses can be accurately simulated with the pole-continuous or wideband Debye models. Attenuation per meter from the dielectric in some PCB materials in a typical stripline is computed and shown in FIGURE 5. The attenuation shows an approximately linear dB/length growth with frequency.

Figure 5. Attenuation per meter from different dielectric materials in a typical stripline.

The dielectric choice may have the most profound consequences on the link performance. For a 112Gbps PAM4 link, for example, the losses per meter at Nyquist frequency 28GHz (a quarter of a bit rate or half a baud rate) may range from 5.1dB/m for the ultra-low-loss dielectric to more than 100dB/m (practically a complete loss of signal) for the regular FR-4-type high-loss dielectrics. Note the ultra-low-loss dielectric with LT = 0.001 is still much more lossy than dielectrics used in cables. This is important to know when you decide to switch from PCBs to cables. There are many ways to reduce the losses on PCB interconnects.

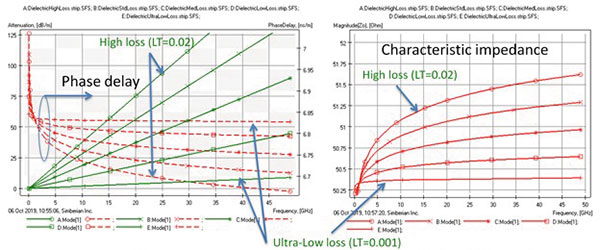

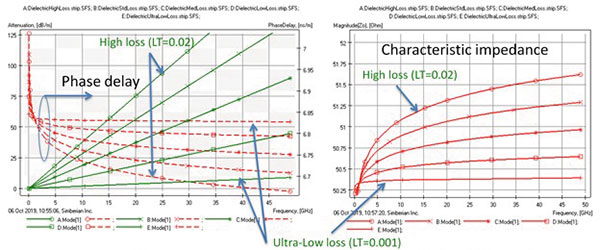

A causal wideband Debye model is used here.5 It can be defined with Dk and LT at one frequency point: 1GHz in this case. The model analytically defines the dielectric constant and loss tangent dispersion from 0 up to 100GHz. The model is causal and includes the dispersion (change in Dk with frequency) of the phase delay and characteristic impedance, as illustrated in FIGURE 6.

Figure 6. Dispersion of phase delay (left graph, red lines) and characteristic impedance (right graph) for dielectrics with different losses (green lines on left graph).

Phase delays are plotted on the left graph on the right axis in ns/m. Characteristic impedances are shown on the right plot in Ω. This simple numerical experiment demonstrates that not only are the frequency-dependent losses included in the model, but it also captures the dispersion of phase delay and characteristic impedance. The model is not causal if it does not include such dispersion.

It also demonstrates that dielectrics with high losses (typically FR-4) have much higher dispersion compared to the ultra-low-loss dielectrics that do not show much dispersion at the frequencies important for analysis of multi-gigabit interconnects. This is not only for the frequency-dependent losses; phase dispersion also causes signal degradation. Signal harmonics are attenuated more at high frequencies and travel with different velocities as well.

Losses in Conductors

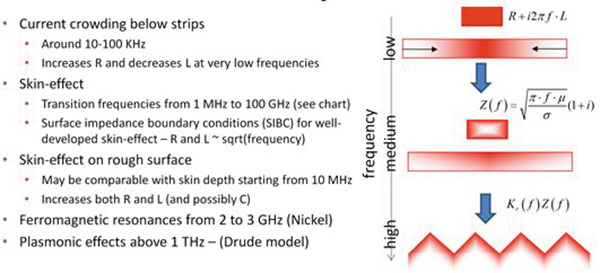

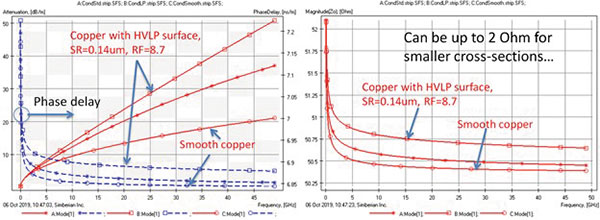

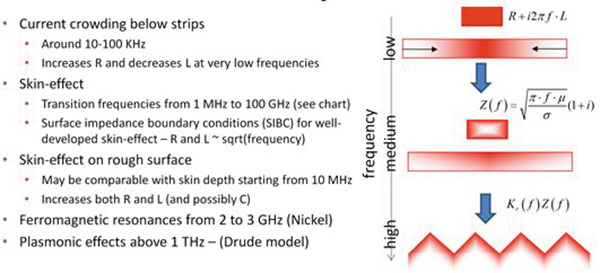

Conductor losses were extensively covered in a tutorial5 and in “How Interconnects Work: Modeling Conductor Loss and Dispersion.”6 Conductor absorption and dispersion effects are summarized and illustrated in FIGURE 7.

Figure 7. Conductor absorption and dispersion effects.

Although the currents in the conductors flow along the signal propagation direction (and back), the power flow vectors within the conductor always point almost exactly perpendicular to the conductor surface. Conductors literally absorb, or “suck,” the energy of the signal and convert it into heat. This is because it is the tangential component of the H field that propagates into the conductor that accounts for the power loss.

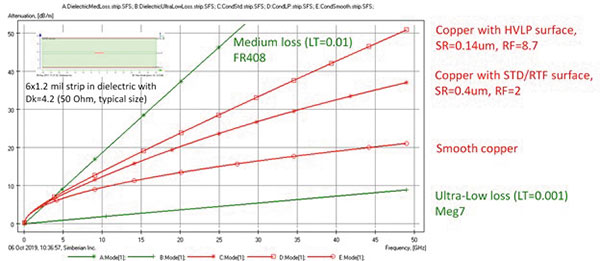

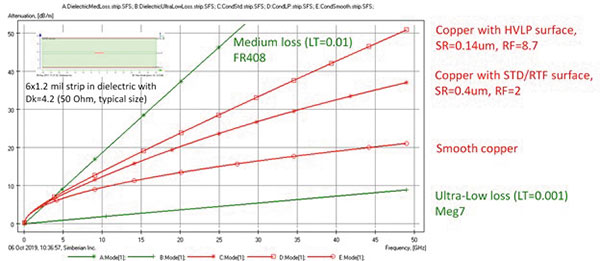

Though conductors are an indispensable part of PCB interconnects – with no viable alternatives so far – additional unavoidable losses and dispersion are related to them. In the case of dielectrics, the absorption can be illustrated with the losses per meter, as shown in FIGURE 8.

Figure 8. Attenuation from typical conductor roughness (red plots) in typical stripline compared with the attenuation due to dielectric losses (green curves).

Dielectric losses for the medium and ultra-low losses are plotted on the same graph as green curves for the comparison. Three red curves are computed for a strip width of 6 mils (about 0.15mm), with smooth copper (no roughness), STD or reverse-treated copper (middle curve) and HVLP copper roughness. Parameters for the roughness models are taken from validation projects and were identified with the measurements.

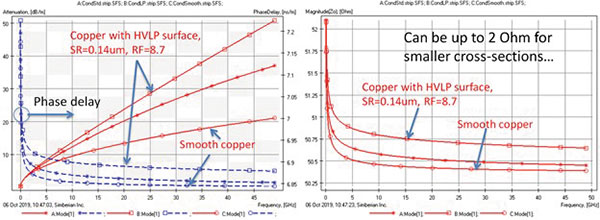

Even with smooth copper, the conductor losses may exceed the dielectric losses for the ultra-low-loss dielectric (valid for a particular cross-section), meaning the minimum possible losses on a PCB are limited mostly by the copper and copper roughness. To have the losses on the PCB closer to cables over a similar bandwidth, larger, smooth traces must be used, reducing current density and overall losses. As a result of the causality requirements, the conductor losses cause dispersion of the phase delay and characteristic impedance, as illustrated in FIGURE 9.

Figure 9. Dispersion of phase delay (blue curves on left graph) and characteristic impedance (right graph) for different copper roughness (red curves on left graph).

Again, if a model does not have the dependency of phase delay and impedance from the roughness model parameters, such a model is not causal and, thus, may not be accurate enough. Always do numerical experiments to verify the dispersion associated with the frequency-dependent loss to see what is in the model. See more on the inductive effect of roughness.6,7

What about the predictability of the absorption or dissipation losses and dispersion? In other words, how do we build models that correlate with the measurements? It depends on availability of the frequency-continuous ultra-broadband models for dielectric and conductor roughness.

Dielectric data from laminate manufacturers can be used to construct such models with sufficient accuracy for preliminary analysis or lower data rates. (They can be defined with a numerical experiment).5 Dielectric models for higher data rates and better accuracy must be extracted from measurements. Parameters for conductor roughness models are usually not available and always must be extracted from measurements. Identification with GMS-parameters8 or SPP light9 techniques with a separation of dielectric and conductor losses can be used to build dielectric and conductor roughness models.

Reducing Power Consumption

Here is how to reduce the signal degradation due to the absorption or dissipation losses:

- Use dielectrics with lower Dk and LT.

- Use more metal to reduce current density. (Wider interconnect traces absorb less energy.) (This is subject to single-mode propagation limit.)

- Use conductors without roughness or “engineered” rough surfaces without additional losses.

Generated signal energy is always turned into heat in conductors, dielectrics or termination resistors, no matter what we do with the interconnect losses. However, interconnects with lower losses reduce the energy required for signal conditioning and restoration. This is valid under one important condition: very low reflections and no coupling. •

References

1. D.R. Stauffer, “Progress and Challenges for Next Generation 400G Electrical Links,” OIF CEI-56G Project Activity, www.ethernetalliance.org/wp-content/uploads/2014/06/Panel-2-Speaker-2_D.-Stauffer.pdf, June 12, 2014.

2. B. Razavi, “Low-Power Techniques for Wireline Systems,” ESSCIRC 2021 – IEEE 47th European Solid State Circuits Conference (ESSCIRC), https://ieeexplore.ieee.org/document/9567882/, September 2021.

3. Y. Shlepnev and V. Heyfitch, “Design Insights from Electromagnetic Analysis and Measurements of PCB and Packaging Interconnects Operating at 6- to 112-Gbps and Beyond,” DesignCon, January 2020.

4. R. Morrison, “Limiting Radiation from Logic Circuit Boards, PCD&F/CIRCUITS ASSEMBLY, October 2018.

5. C. Nwachukwu, Y. Shlepnev and S. McMorrow, “A Material World: Modeling Dielectrics and Conductors for Interconnects Operating at 10-50Gbps,” DesignCon, 2016.

6. Y. Shlepnev, “How Interconnects Work: Modeling Conductor Loss and Dispersion,” Simberian App. Note #2016_01, 2016.

7. “How Interconnects Work: Rough Conductor Currents and Internal Inductance,” Simberian video #2017_09.

8. Y. Shlepnev, “Broadband Material Model Identification with GMS-Parameters,” IEEE Conference on Electrical Performance of Electronic Packaging and Systems, 2015.

9. Y. Shlepnev, Y. Choi, C. Cheng and Y. Damgaci, “Drawbacks and Possible Improvements of Short Pulse Propagation Technique,” IEEE Conference on Electrical Performance of Electronic Packaging and Systems, 2016.

Yuriy Shlepnev is president and founder of Simberian (simberian.com), where he develops Simbeor electromagnetic signal integrity software. He has a master’s in radio engineering from Novosibirsk State Technical University and a Ph.D. in computational electromagnetics from Siberian State University of Telecommunications and Informatics. He was the principal developer of electromagnetic simulator for Eagleware and a leading developer of electromagnetic software for the simulation of signal and power distribution networks at Mentor Graphics. His research has been published in multiple papers and conference proceedings; This email address is being protected from spambots. You need JavaScript enabled to view it.