The proper design of the power distribution network, coupled analysis in the early design phases, can eliminate most power integrity issues.

A number of recent trends – the growing number of different voltages on a design, coupled with increasing power demands from integrated circuits (ICs), as well as the ever-present issues of increasing operating frequency and the need to reduce product cost – have caused power integrity (PI) issues to become more and more of a problem in today’s electronic designs. Since both PI and signal integrity (SI) problems often turn up as data errors, PI issues are frequently misdiagnosed as SI problems. Thus, an understanding of power delivery issues is essential to the success of a PCB design.

The goal in designing a power distribution network (PDN) for a PCB is simple: minimize the impedance between power and ground for your frequency range of interest. Successful execution of that design goal is not quite as simple.

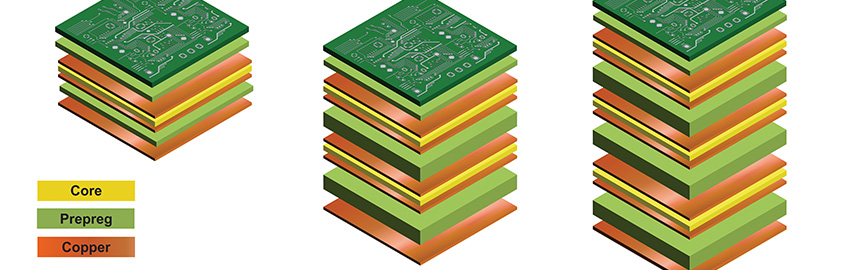

The PDN consists of: a combination of the DC-to-DC converter or voltage regulator module (VRM) supplying voltage to the rail; the decoupling capacitors tied between power and ground; the planes and/or traces carrying power; on-chip decoupling; and the pins and vias connecting all these elements together. The VRM is very effective in providing a low impedance path between power and ground, up to around 1MHz. For the remainder of frequencies, the low impedance between power and ground must be provided by the board and chip capacitances.

The board and chip capacitances combine in parallel but are each limited by their parasitic inductances and resistances. Without parasitics, all the capacitances would combine to make one large capacitance, equating to a lower impedance with increasing frequency. Unfortunately, each capacitance is only effective in a given frequency range, limited by its parasitic inductance. Because the amount of capacitance between planes is typically limited by area and spacing, the plane capacitance does not equate to a low impedance until higher frequencies. As such, each of the board capacitances is only effective for a certain frequency range and must work together to provide a low impedance between power and ground across the entire frequency range. An example plot of impedance versus frequency is shown in FIGURE 1.

A factor limiting the effectiveness of the board capacitances is chip/package inductance. This additional inductance adds to the parasitics of the board capacitances, making them ineffective above about 1 GHz. Above 1 GHz, the on-chip capacitance (not limited by the inductance of the package) provides the low impedance path between power and ground. As such, board decoupling is typically analyzed between about 1 MHz and 1 GHz, and board PDN design is focused at minimizing the impedance between these frequencies.

Maintaining a low PDN impedance introduces a number of benefits. The most direct benefit is minimizing the amount of voltage ripple at the IC supply pins. In fact, the tolerable amount of voltage ripple at the IC supply pins is what determines the maximum allowable PDN impedance. The PDN impedance requirement may be calculated using the following formula:

Zpdn = (% ripple * V) / Imax

where V is the rail voltage and Imax is the peak current draw of the IC. As such, ICs with higher current draw and lower operating voltages require a lower PDN impedance.

Another benefit of a low PDN impedance is the reduction of noise propagation throughout the board. Power pins, signal pins and vias can introduce noise onto the planes that can propagate around the entire PCB. The presence of low impedance paths between power and ground facilitates better flow of return currents.

At DC, the problem becomes much simpler, but failures can be much more severe. The goal is still to minimize the impedance of the PDN, but at DC, the main concern is providing an adequate amount of metal to distribute up to tens-of-amps of current. With planes being partitioned up to accommodate the growing number of different voltages on a PCB, this can be quite a daunting task.

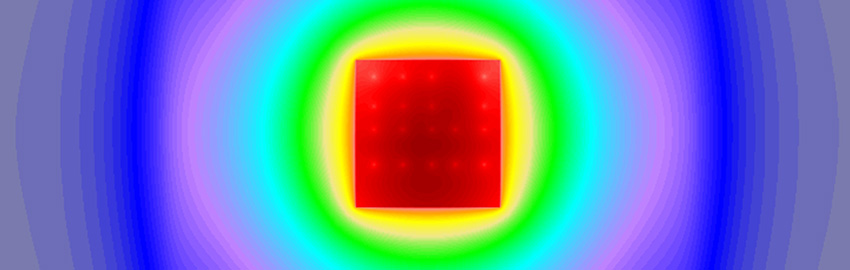

Analysis of plane shapes within the PDN can be very useful in identifying areas of low voltage. Areas of the board where voltage dips below a certain minimum threshold can lead to IC malfunction, including, but not limited too, signal integrity problems and logic errors.

Of equal concern are areas of high current density on the board. These can be caused by neckdowns due to the partitioning of the plane, but they are also common in dense connector and IC pinfields, where antipads eliminate a great deal of the copper on plane layers. Areas of high current density lead to voltage drop but can also lead to board failure. Analysis of the PDN at DC will also produce this useful current density information. It is also important to monitor current through vias connecting planes together or VRMs to planes. Vias can act as similar neckdowns and areas of high current density, resulting in similar failures.

Through an understanding of proper design of a power distribution network, coupled with analysis early in the design phases, severe issues with power integrity can be avoided. This ultimately results in meeting schedule and budget goals, while designing products that are more reliable and last for many years to come. PCD&F

Patrick Carrier is a technical marketing engineer for Mentor Graphics.