Is Fan-out Wafer-level Packaging Right for Your Product?

New CAD tools feature virtual prototyping for evaluating effects of packaging architecture on functionality, cost, weight and size.

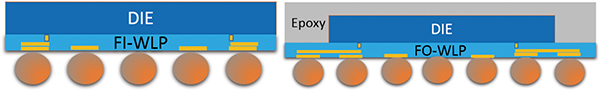

Fan-out wafer-level packaging (FO-WLP) technology has picked up considerable momentum since it was selected by Apple for use in the iPhone 7. FO-WLP establishes die-to-die and die-to-ball grid array (BGA) connectivity directly through packaging redistribution layers (RDLs), eliminating the packaging substrate used in more-established flip-chip and wafer-level chip scale packages (WLCSP). The advantages of FO-WLP include the ability to support more I/O, a smaller vertical footprint that often makes it possible to reduce product form factor or stack more components, a reduction in costs by eliminating the interposer and insertion of through-silicon vias (TSVs), and improvements in electrical and thermal performance because the transistors drive less metal length.

Figure 1. Fan-in vs. fan-out wafer level packaging.

Achieving these advantages requires overcoming some significant challenges. First is conducting extensive tradeoff studies to determine whether the FO-WLP architecture is right for the product from a functionality, price, performance, size, weight and style standpoint. Second is integrating the normally independent design processes for the chip and package in order to optimize FO-WLP design, with its greater-than-ever interdependencies between the chip and package. A product-centric design process makes it possible to weigh the impact of FO-WLP versus competing package technologies in terms of these attributes and more. A new generation of integrated chip/package/board co-design tools makes it possible to holistically optimize FO-WLP designs to a greater degree than was possible in the past by considering the system-level impact of each design decision.

Advent of FO-WLP. Substrate-based packaging first emerged a couple decades ago as an alternative to lead-frame packages and has since grown to account for 68% of integrated circuit package value, according to Prismark Partners. Larger chips such as central processor units (CPUs) and mobile silicon-on-chips (SoCs) have generally been packaged via flip-chip methods in which inputs and outputs are connected with solder bumps to a substrate, which is in turn attached to a printed circuit board (PCB). Connections are formed over the surface of the die area, while the use of wire bonds limits connections to the package perimeter.

To meet the needs of thinner mobile devices, WLCSPs have been developed (FIGURE 2). They differ from flip-chip packages primarily in that the die is mounted directly on the PCB. The reduced form factor provided by mounting the die directly on the PCB has vaulted WLCSP to the leading position for smartphones and other products where space is at a premium. In WLCSP chips, I/Os are generally fanned in across the die surface using RDL buildup layers to produce an area array, and solder bumps are formed at the terminals by ball drop or plating. But as die footprints shrink and I/Os increase, WLCSP has run into limits on the number of I/Os it can support, typically about 200 I/Os at 0.6mm profiles, according to Yole Développement.

Figure 2. Expansion of advanced packaging architectures. Source: TSMC

FO-WLP enables redistribution of I/Os beyond the chip footprint, differing from WLCSP in several key areas. The FO-WLP process typically starts when individual dies are placed on double-sided tape sitting on a silicon carrier. The die is covered with a mold compound, and the carrier and tape are removed, leaving the die embedded in the mold. The wafer is turned over; an RDL is created, and solder balls are formed on top, just as in a WLCSP. The extra panel surface area around the chip permits I/Os to be both fanned in over the chip and fanned out across the mold compound, making it possible to accommodate a larger number of I/Os.

One major advantage of FO-WLP, especially in mobile applications, is that the elimination of the substrate reduces the vertical footprint by an average of 40% compared with WSCLP, enabling thinner products or making it possible to stack more components in the same form factor. The elimination of the interposer and TSVs also provides a cost reduction and eliminates concerns on the effects of TSVs on electrical behavior. The reduced path to the heat sink also helps improve thermal performance.

Challenges in implementing FO-WLP. Yet, FO-WLP is far from a universal solution. When considering whether fan-out architecture is right for a product, conduct trade studies to optimize routability, such as by trading off large I/O-count fan-out devices vs. smaller I/O-count fan-in devices from a size, cost and performance standpoint. The routability and cost of various bump pitch technologies and the potential for die stacking also need to be taken into account. At the same time, tradeoff studies should be conducted to optimize signal quality, power delivery and thermal performance in the early stages of the design process. Memory bandwidth and latency should be considered at this stage, along with checking for thermal hot spots.

The greater complexity of FO-WLP packaging technology is creating vast new challenges for not only package designers, but also IC and PCB designers who must integrate the package into their own work. Traditional system design relies on separate tools that address the IC, package and PCB in standalone environments.

These flows lack system-level planning, visualization, design and analysis. Co-design is challenging because designers typically only have a view of their own component, and file interchange formats used to exchange data between these environments are often antiquated and deficient, missing useful design data or are proprietary and not broadly supported. Design databases used in planning are not interoperable with databases used for review and analysis, so it is difficult to guarantee decisions made during planning are carried through to the final product. With the lack of tool integration, companies have often reverted to workarounds, such as using spreadsheets and generic office productivity tools to perform planning and feasibility studies and to define the tool interfaces and data transfer.

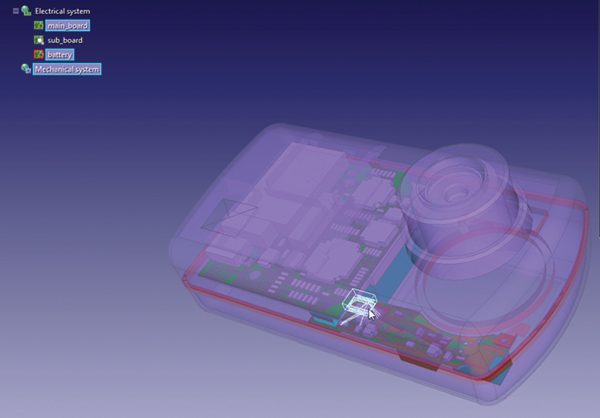

New generation tools aid FO-WLP implementation. The tradeoff study challenge is being addressed by a new virtual prototyping process (FIGURE 3), where the effects of packaging architecture on functionality, cost, weight, size, and more can be evaluated collaboratively with the ability to make tradeoffs before committing to detailed design. In the very early stages of the process, the functional design is defined using reuse blocks, BoM-based functional blocks or any existing detailed design. The most common approach involves starting with the previous generation of the product. The functional design moves to a packaging technology planning activity, where it is possible to evaluate alternative packaging technology in the context of the overall system design. Using a product-level planning tool, the design team can consider the impact of different packaging technologies from multiple product views: functional, physical, geometric and parametric. Cost and weight targets, among other factors, can be validated before committing to detailed design.

Figure 3. Product-based virtual prototyping.

After the basic packaging architecture decision is made, an integrated 3D chip/package/board co-design environment makes it possible to holistically optimize the IC, package, board and enclosure in a single view, so all those working on the project can see their piece of the puzzle in context of the full product (FIGURE 4). For example, engineers can perform a feasibility study of different numbers of package layers, while considering the routing of the RDL on the IC side and the escape route on the PCB side in a single design view. Automatic routing of the chip RDL and package escape permits rapid pathfinding feasibility, improves completion times and allows users to optimize die bump placements. The ability to conduct system-level co-design of the chip and package makes it possible to optimize bump and ball placement, I/O placement and pin assignment to lower chip, package and PCB layer counts, even in nontraditional structures with routing complexity such as FO-WLP and WLSCP.

Figure 4. Co-design environment for chip, package, and board to enable package path-finding.

An integrated design-for-manufacturing tool makes it possible to verify the design to vendor technology-specific manufacturing checks for fabrication and assembly during layout. The benefits include reducing RDL, interposer/substrate and package layer count, while optimizing signal performance and improving time to tape-out.

Conclusion. FO-WLP offers the potential to increase IO counts, provide a smaller vertical footprint, reduce packaging costs and improve electrical and thermal performance. Taking advantage of these benefits requires exhaustive tradeoff studies in the conceptual design process to evaluate whether FO-WLP is a fit, and even more detailed studies as the project proceeds in order to optimize the IC, package and PCB designs with interactions between the different design elements taken into account. Product-centric design tools make it possible to consider the effects of alternative packaging approaches on functionality, price, size, weight, etc. in the early stages, without investing the time that would be required to fully define the design. Subsequently, once the decision on package architecture is made, 3D chip/package-board co-design provides tight collaboration between design environments to improve design quality by enabling all members of the design team to see the impact of tradeoffs on the project requirements, resulting in a compelling product.

is solutions architect at Zuken (zuken.com); This email address is being protected from spambots. You need JavaScript enabled to view it..